存算一体或存内计算是将存储与计算完全融合,直接利用存储器进行数据处理或计算。在传统的冯诺依曼架构下,数据的存储和计算是分开的,由于存储和计算的性能存在加大的差距,处理器访问存储数据的速率远远小于处理器计算速率,数据在内存与主存之间搬运的过程其能耗也远远高于处理器的计算所消耗的能量。

从NPU和TPU的架构设计可以看出,其本质都是在解决数据高效访存的问题,只是实现方式略有差异。总结看来主要包括了:

通过提高通信带宽实现数据的高速传输和降低功耗。

将数据存储尽量靠近计算单元,从而降低数据搬运的延迟和功耗,比如多级缓存和片上存储。

提高数据在时间和空间上的复用效率,减少数据与主存的通信次数。

存算一体通过将计算单元和存储单元集成在同一个芯片,让存储单元具有计算能力,使得计算可以在存储器单元内完成,极大的降低了数据搬运带来的延迟和功耗,其特别适用于深度学习这种需要大规模的数据搬运和大规模并行计算的场景。

存内计算

存内计算一般包括数字计算和模拟计算两种实现方式,模拟计算能效高但计算精准度低,数字计算计算精准度高但功耗较大,当前主流的存内计算主要还是以模拟计算为主。

模拟存内计算主要基于物理定律在存算阵列上实现乘加运算,以忆阻器上的矩阵乘法MxN为例,运算前,先将矩阵M按行列位置存入忆阻器,在输入端矩阵M使用不同电压值来表示,根据欧姆定律和基尔霍夫定律在输出端可以得到对应的乘加后电流矢量,多个存算阵列并行,便可完成多个矩阵乘法计算。

数字存内计算是通过在存储阵列中加入与或门、乘法器、加法器等逻辑计算电路,使存储阵列不仅具备存储功能还具备计算能力。由于需要为每个存储单元增加了逻辑电路,所以其在芯片面积上并不占优势,限制了其计算能力的拓展,因此,当前数字存内计算实现更多的采用先进工艺来实现,由于工艺和成本的因素,其应用范围受到了比较大的限制。

类脑计算

基于人脑的脉冲(spiking)模拟计算框架下的脉冲神经网络 (SNN)有望在实现人工智能的同时降低计算平台的能耗。

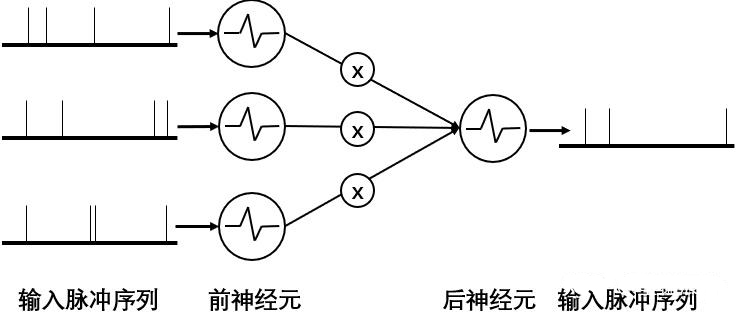

在SNN模型中上游神经脉冲Vi通过突触权重Wi调节,在给定时间内产生的合成电流 等效于点积运算。从图例可以看出,脉冲计算通过电流的进出模拟神经元计算过程,整个系统基于事件驱动,深度学习网络计算又是高度稀疏的,所以通过脉冲通信和计算可以实现极低能耗下大规模并行计算。

脉冲计算示例图

从脉冲计算过程可以看到,脉冲计算的硬件结构需要存算一体的体系设计将神经元和突触阵列紧密放置在一起。所以当前的脉冲神经网络芯片基本都采用模拟存内计算的存算一体的架构设计。

技术挑战

存内计算虽然有很多的优势,但商业应用上还面临着诸多挑战,其在器件研发、电路设计、芯片架构、生成制造、EDA工具链以及软件算法等环节都还面临不少的问题需要解决和突破,整体技术成熟度较弱。

存算一体化需要同时满足存储和计算两者的设计需求,比如存储单元的可靠性、擦写次数、器件一致性等,计算单元的响应速度、功耗等。从当前半导体电路设计和制造工艺,要同时兼顾难度较大。

受限于工艺和芯片面积,当前商用存内计算的芯片算力较小,能支持的算力和算子有限,所以能力支持的神经网络算法也有限,通用性较差。

当前主流的模拟存内计算的计算精准度较差,计算结果不准确会导致实际计算结果与理想结果产生偏差。数字存内计算的虽然计算精准度高,但运算开销较大。

当前逻辑单元电路实现还是以基于二进制数字精准运算为主,模拟运算在理论和电路实现上相对缺乏,导致模拟计算的芯片实现难度较高。

存内计算芯片设计与常规芯片有较大差异,现有的EDA工具无法提供标准单元库以供芯片设计者使用,缺乏大规模存算阵列的快速开发工具导致产品化效率低。

郑重声明:文中仅代表作者观点,不代表本公司观点,本文版权归原作者所有,转载文章仅为传播更多信息之目的,如作者信息标记有误,请第一时间联系我们修改或者删除,感谢您的关注!