寒武纪是国内最早一批研究AI芯片公司,其AI芯片NPU (Neural network Processing Unit)的设计源于其早期一系列的AI芯片架构研究,主要包括DianNao、DaDianNao、PuDianNao、ShiDianNao、Cambricon-X等一系列研究成果。

DianNao

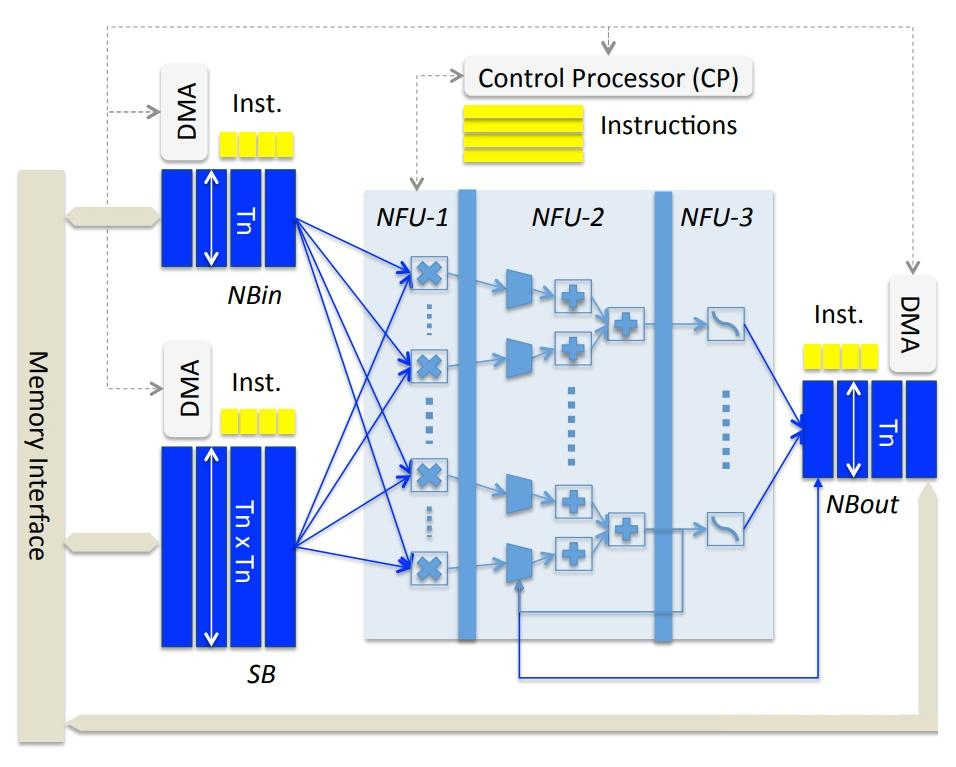

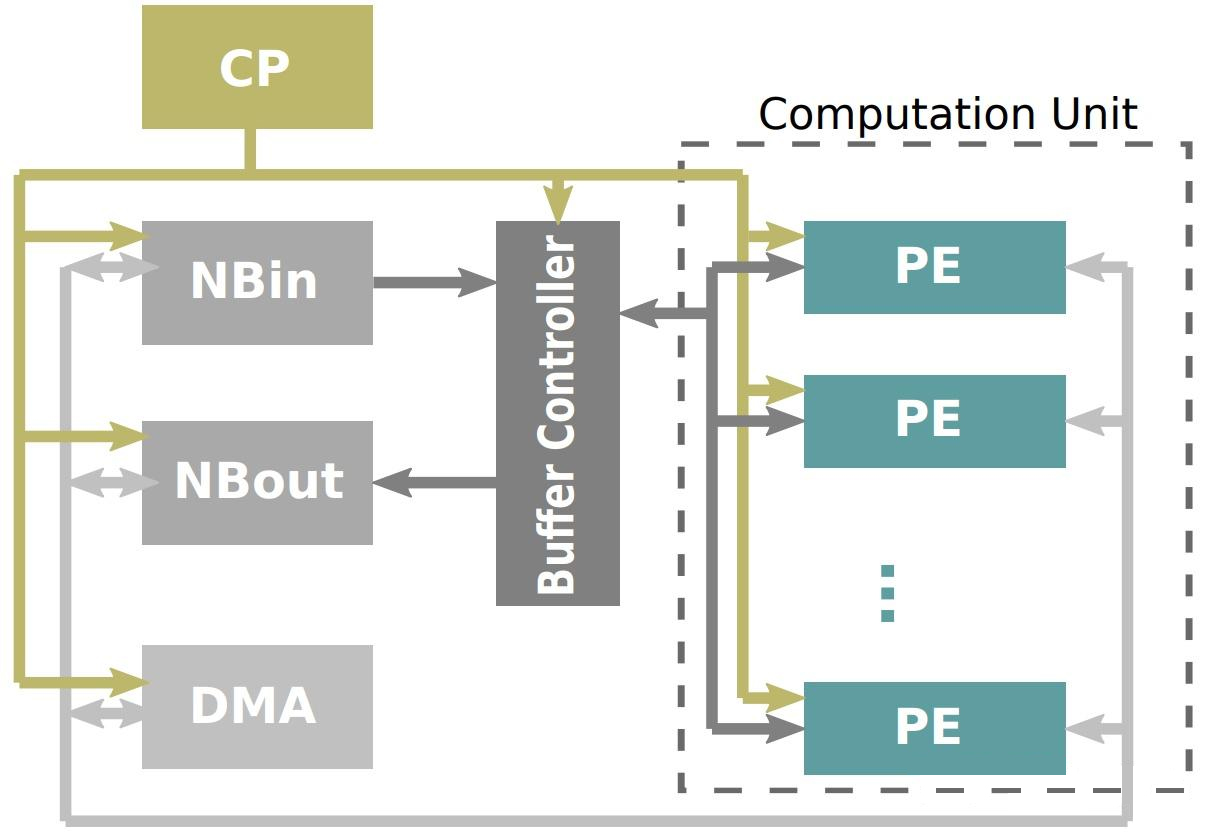

DianNao是AI芯片设计中开创性研究,是为了实现处理大规模深度学习网络运算而设计的专用芯片。如图所示,芯片采用彼此分离的模块化设计,主要包含控制模块(Control Processor, CP)、计算模块(Neural Functional Unit, NFU)和片上存储模块三部分。其中,片上存储模块又分为用于存储输入数据的NBin、用于存储输出数据的NBout以及用于存储神经网络模型权重参数的SB,这三块存储均为片上存储,以实现低延时和低功耗。

目前深度学习网络参数量都非常的大,片上缓存区容量大小一般都远小于参数量,无法将整个网络的参数全部放入片上存储。所以DianNao架构设计采用了分时复用方法,每次只加载和执行网络一部分,模型参数会分批次的加载到SB中,每个网络层的输入数据也会分批次的加载到NBin中,每层计算结果则写入到NBout中。NFU (Neural Functional Unit)是由三级流水线组成计算单元,主要负责完成神经网络的核心计算逻辑,比如乘法操作、加法操作和非线性函数变换等。

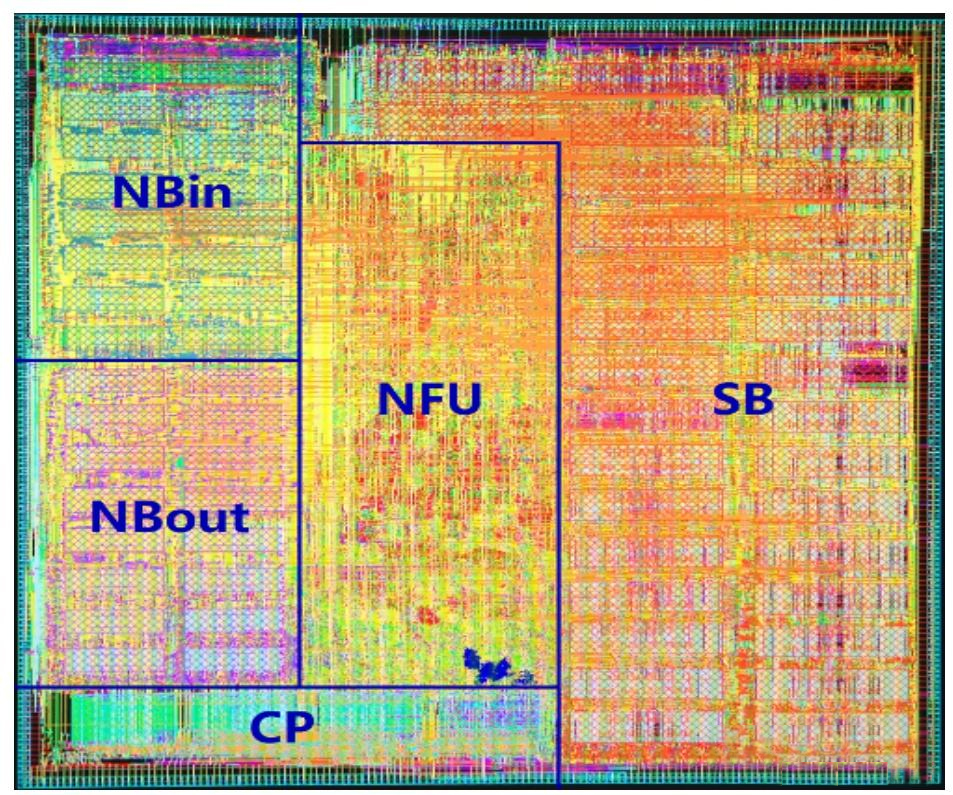

Diannao布局(65nm)

拆分成不同的模块的设计可以在功耗和性能上找到更佳的设计平衡点,其中,输入存储(NBin),权值存储(SB),输出存储(NBout)各自单独实现,一方面可以根据不同数据访问特性设置不同传输带宽,另一方面还可以实现类似Cache的功能,即处理器在对当前一组数据进行计算的同时,可以通过DMA启动下一组数据或参数的加载。如图所示,每个存储单元配备有一个DMA和一个指令缓存FIFO,通过将计算过程和数据传输过程解耦实现数据高效预取,只要前一条指令使用完了数据,后一条指令就可以开始数据传输,而不需要等待前一条指令的计算完成。

计算单元NFU包括三个阶段并以流水线形式执行,是神经网络的核心计算模块。NFU-1是一个16x16的并行乘法单元,即一个周期可以同时执行256个乘法操作,NFU-2包含16个加法树,每个加法数包含15个加法器,加法器按照8-4-2-1的结构排列,NFU-3包含16个激活函数单元。从整体看,NFU的所有资源被划分成16份,NFU-1中每一份包含16个乘法器,同时执行得到16个乘法结果,然后送入NFU-2中加法树,每个加法树中先由8个加法器对16个数执行加法操作得到8个结果,再依此由4-2-1个加法器对前面的结果进行加法操作,最终得到一个累加的结果之后再送入NFU-3的激活单元进行计算。

Diannao架构

DaDianNao

DaDianNao针对主流神经网络模型提出了一种可以承载较大尺寸模型的芯片架构,主要针对服务器端的AI高性能训练和推理计算任务。DianNao架构虽然在性能和功耗上相比CPU取得了比较明显的改善,但其也存在一些问题和限制。DianNao主要通过三个片上buffer (NBin, SB, NBout)进行数据进行分块处理,将不同类型的数据块存放在不同的片上存储中,其可以根据不同类型数据特性和复用进行针对性优化,使芯片与主存之间的数据搬运次数和效率达到最优,进而实现提高芯片整体性能和降低功耗的目的。DaDianNao则是为了处理大规模神经网络模型而设计的AI芯片架构,其采用了基于tile和node的多芯片组设计来解决大模型的参数在芯片和内存通讯而带来带宽和功耗的问题。

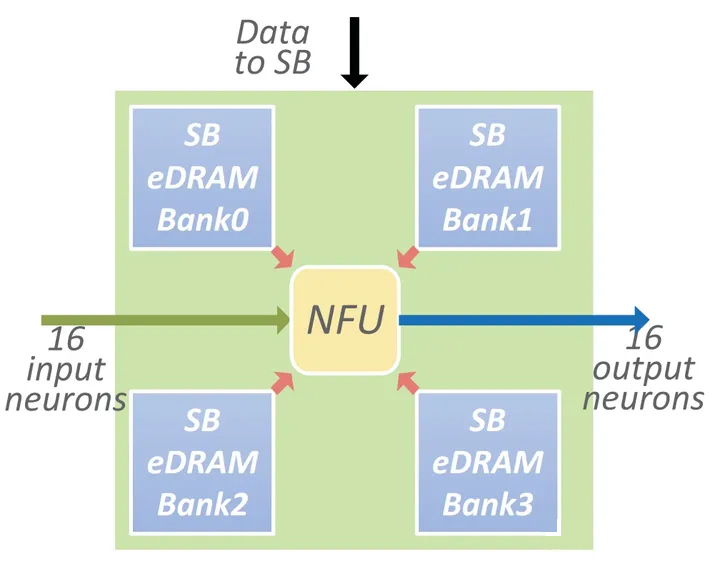

如图所示,每个tile包含一个NFU,四个eDRAM Bank和一个与中央eDRAM相连接的I/O接口,模型参数存放在离NFU更近的eDRAM存储区域中,输入输出数据则需要通过访存操作完成数据加载。tile使用eDRAM代替SRAM存储模型参数,使其在存储密度、访存延迟和功耗之间针对大模型的资源需求上得到了更好的平衡。

tile架构

当模型的参数远远大于输入/输出数据时,将大尺寸模型参数布署在离计算部件更近的eDRAM中,以减少计算过程中的访存延时,而将尺寸较小的输入/输出通过访存操作进行加载、可以减少有效访存开销,将SB拆分放置以减少数据访问冲突,进一步减少访存延迟。

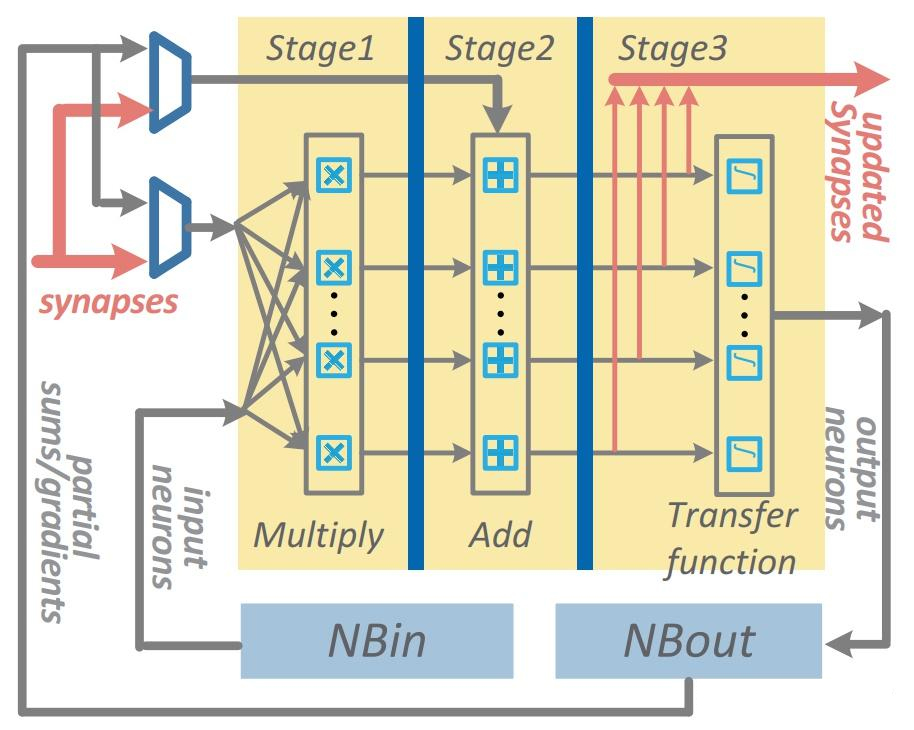

DaDianNao的NFU相比于DianNao更复杂,并增加了针对模型训练而设计的功能模块。改进后的NFU计算单元如图所示,在每个tile中计算的中间值会放在tile的本地eDRAM中,计算完毕后再将其输出。

DaDianNao NFU架构

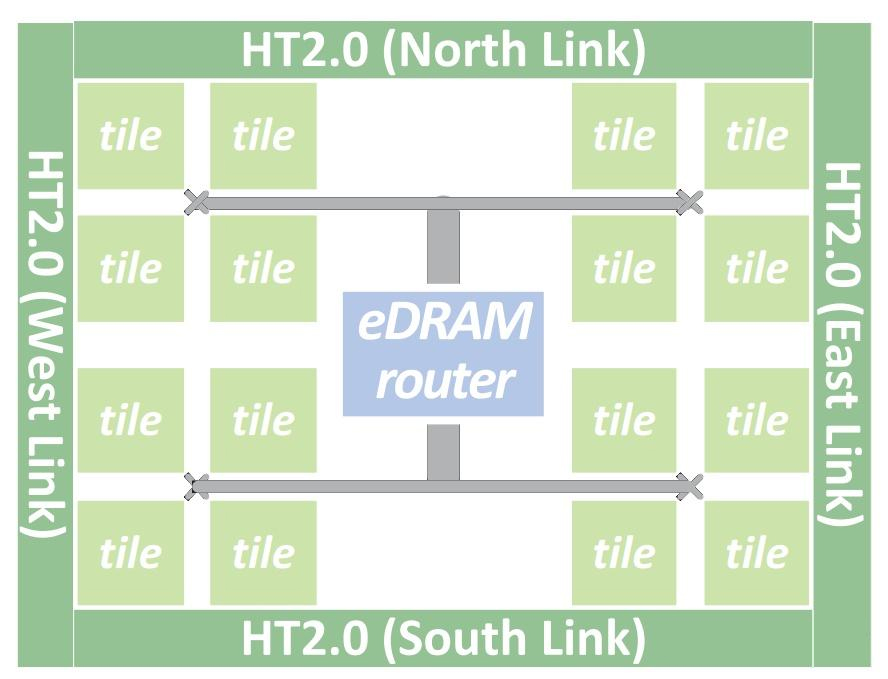

在多芯片组中一个芯片为一个node,如图所示,一个node包含16个tile和两个中央的eDRAM Bank,他们之间通过Fat-tree相互连接。这两个中央eDRAM存储区一个用于将输入数据广播到每个tile,一个用于收集所有tile的输出结果。

node结构

在多芯片系统中,每个芯片的四周集成了四组HyperTransport 2.0的通信通道,用于芯片与四周的芯片相连组成一个多芯片系统。相比与DianNao,在实现相同算力的条件下,其芯片面积减少了28.5%,将参数储存在片上的eDRAM中降低了片外访存的带宽需求,参数存储单元放在离NFU更近区域,并进行分块存放,不仅减少了数据访问的冲突也提高了数据传输速度。

ShiDianNao

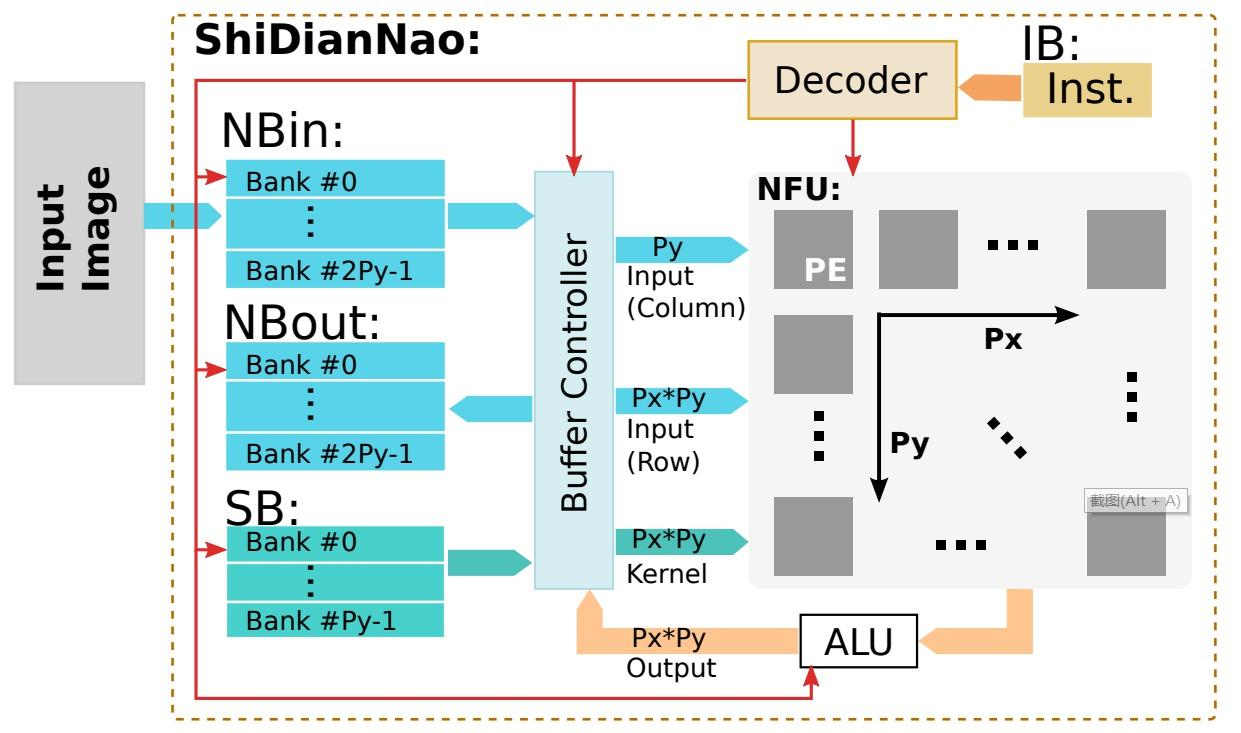

ShiDianNao是基于CNN模型实时采集图像进行计算处理的专用AI处理器,芯片与图像传感器直接相连接,图像数据不需要经过DRAM存储器就可直接输入到芯片的处理单元进行处理。如图所示,ShiDianNao中的存储部件与DianNao类似,分为NBin、NBout和SB,分别用于存储神经网络的输入数据、输出数据和权重参数。运算单元包括神经网络专用计算单元NFU和通用逻辑运算单元ALU。ShiDianNao在存储单元和计算单元中间引入了一个缓存区域Buffer Controller,用于缓存输入数据和汇总NFU的计算结果以提高处理器的并行度。

ShiDianNao架构

ShiDianNao中的NFU由Px*Py的二维PE (Processing Elements)阵列组成,支持数据在PE之间流动,NFU读取参数和输入数据后分发给不同PE处理,之后NFU会收集汇总处理后的结果,计算结果会输出给一个ALU单元,ALU里包含了一些非线性激活函数的硬件实现,ALU的计算结果再通过Buffer Controller最终写入到NBout里。

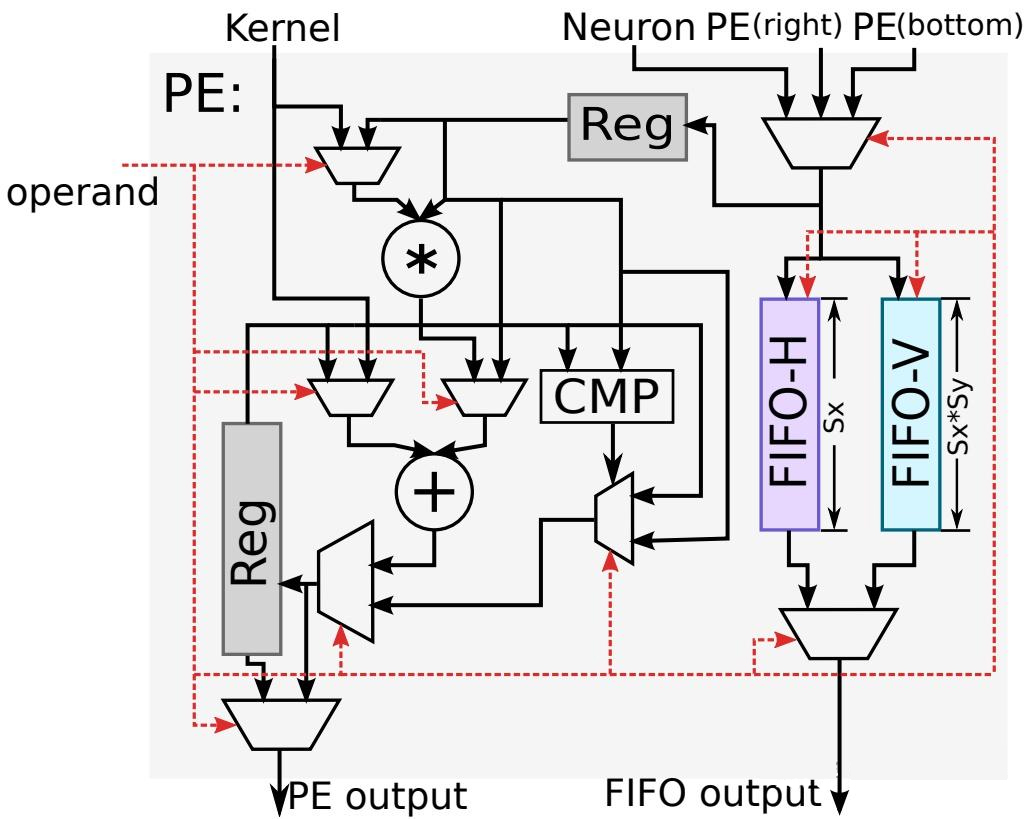

每个PE单元还有内部的存储结构,以支持PE之间的数据传输。如图所示,每个PE内部由一个乘法器、一个加法器、若干个寄存器、两组用于数据交互的FIFO等部件组成,其中FIFO-H用于存储水平方向数据,FIFO-V用于存储竖直方向数据。每个PE有三个输入接口,一个是用于接收控制信号operand,一个用于接收权重参数Kernel,还有一个用于接收输入数据,其来源可能是右边PE的输出、下边PE的输出或者NBin。每个PE有两个输出,一个用于将计算结果写到NBout,另一个则用于传输给邻居PE以实现不同PE之间的数据传输。由于卷积运算的相邻滑动窗口之间有着大量的重复数据,通过FIFO-H和FIFO-V两个模块接收相邻PE的数据,实现PE间数据传输和复用,可以极大的减少存储带宽的需求,Kernel数据以广播的形式发送到每个PE参与计算。

ShiDianNao PE架构

PuDianNao

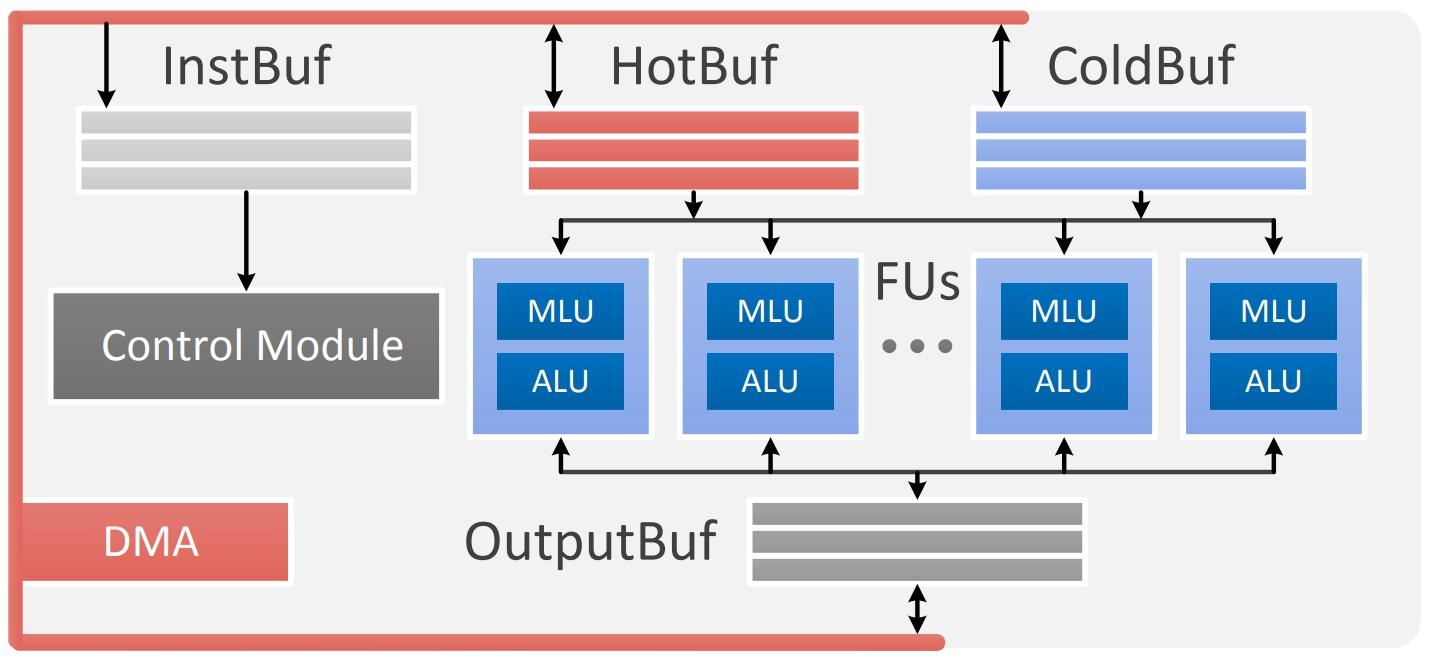

PuDianNao在分析了各类机器学习算法在访存行为、计算模式上的差异后从更细粒度的数据重用和计算操作上进行了重新设计,使其能能够支持包括KNN、DNN、SVM、Classification Tree等七种经典机器学习算法的AI处理器。

PuDianNao的架构由若干个FUs (Function Unit)单元,三个不同用途的数据缓存模块 (Hot Buffer, Cold Buffer, Output Buffer),一个指令缓存模块(Inst Buffer)和一个控制模块(Control Module)等组成。 整体来看,在分析和总结了不同机器学习特性的基础上,PuDianNao通过定义专用硬件来提升整体计算性能,通过设计特定的缓存模块来提升访存性能。

PuDianNao架构

Cambricon-X

Cambricon-X主要是针对于神经网络中的稀疏性的特点,进行设计的芯片架构。神经网络中的稀疏性主要分为两种,一种是权重参数的稀疏化,另一种是特征向量的稀疏化。Cambricon-X实现的是权重的稀疏化在硬件实现上的支持,特征向量稀疏化由于随输入数据动态变化,使得其管理和控制的逻辑更为复杂,所以Cambricon-X在硬件上没有这一方面进行支持。

神经网络中的稀疏性一方面可以通过稀疏化训练(比如在训练过程中增加正则化和门控函数等)增加模型参数的稀疏性,另一方面还可以通过剪枝算法进一步提升模型的稀疏性。韩松等人的研究证明,通过剪枝技术可以在基本不影响模型计算精度的情况下将深度学习网络模型权重系数去掉90%以上。虽然算法上可以实现模型的高度稀疏化,但这种稀疏化常常是不规则的稀疏,目前的主流的CPU和GPU等硬件平台都无法对不规则的稀疏进行有效的运算加速,所以性能上仍然受到比较大的限制。

Cambricon-X提出了一种针对稀疏神经网络高效运算的硬件实现方案。如图所示,Cambricon-X的架构设计与DianNao系列的设计由很多相似之处,主要包括控制处理器CP,缓冲区控制器Buffer Controller,两个数据缓冲区NBin和NBout,内存访问模块DMA和计算单元Computation Unit,其中计算单元由多个处理元素(Processing Elements, PE)组成。其主要的区别在于中间Buffer Controller模块,这个模块是针对稀疏加速器特别引入的模块,也实现稀疏访存和计算的核心。

Cambricon-X架构

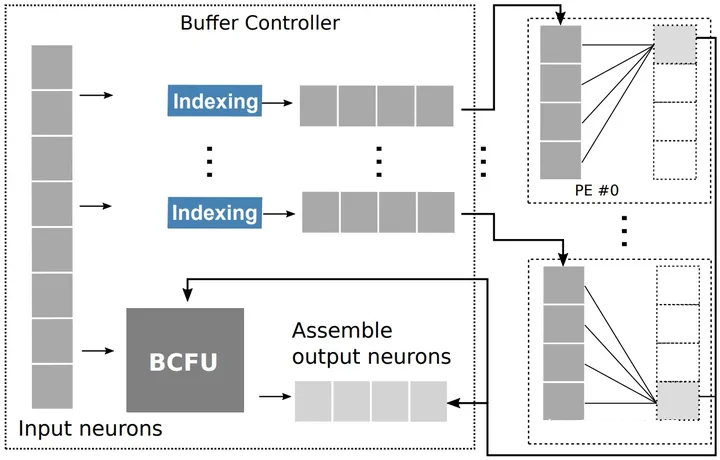

为了实现网络参数的稀疏化计算,需要将数值为0的数从权重参数中剔除,并记录参数中非0数据的位置,在计算时先从输入数据中挑选出非0权重对应位置的数据,重新排列后的数据与非0参数一并传给对应的PE执行计算操作。在Buffer Controller主要由Indexing Module (IM)和一个专用功能单元BCFU组成,稀疏数据的筛选主要是由IM来完成的,BCFU主要用于存储待IM筛选的数据。

Buffer Controller架构

IM模块的引入实现了仅将索引后的数据传给PE完成后续的计算操作,一方面索引后的数据量在稀疏网络中占比很小,可以极大的减少BC区与PE之间的带宽需求,另一方面索引后的数据在BC区域完成了数据的重排,在PE上也仅需要执行较少的并行计算操作。

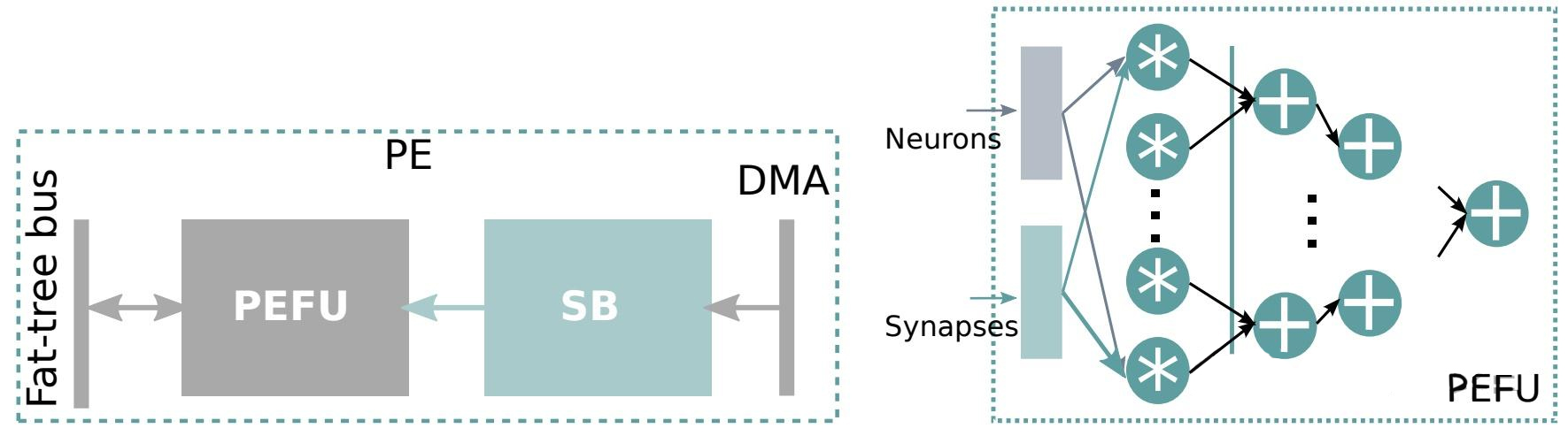

PE是神经网络计算单元,如图所示,SB为参数缓冲区,用于缓存网络的权重参数,虽然片上存储空间有限无法将所有权重参数加载进来,但是权重有更强的重复访问特性,所以SB设计依然可以极大的减少数据访存带来的开销。PEFU是计算逻辑的硬件实现,其本质是神经网络计算所需的一组乘加器的组合连接。

Cambricon-X PE架构

总结

综上所述,从Diannao系列和Cambricon-X来看,针对AI计算同时具有数据密集型和计算密集型的特性,NPU主要通过增加更多的并行计算单元来实现更高效率的计算,同时将计算靠近存储的方式来解决数据高效访存的问题。根据不用的应用场景和算法特性通过软硬件协同设计的思路来设计特定领域的AI芯片,并在性能、功耗、面积等指标之间找到最佳的平衡点。

郑重声明:文中仅代表作者观点,不代表本公司观点,本文版权归原作者所有,转载文章仅为传播更多信息之目的,如作者信息标记有误,请第一时间联系我们修改或者删除,感谢您的关注!