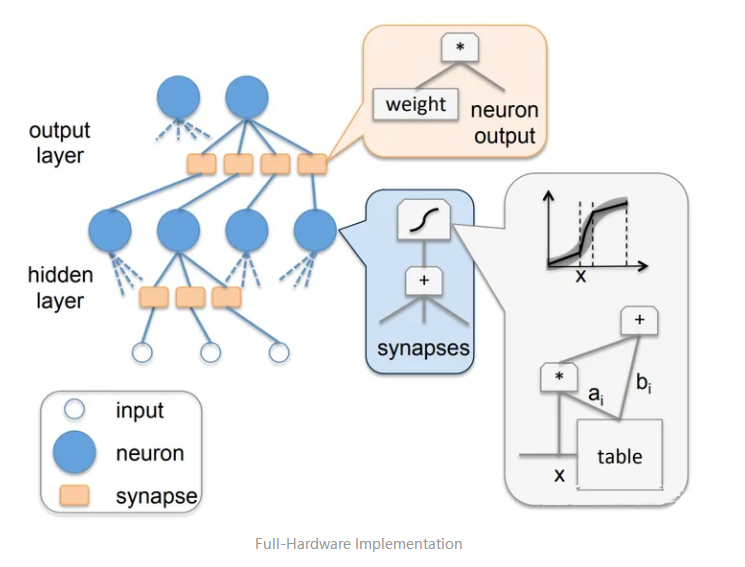

AI芯片最简单直接设计思路就是将神经元直接映射到硬件芯片上,如图所示,全硬件实现方案(Full-Hardware Implementation)将每个神经元映射为一个逻辑计算单元,每个突触映射为一个数据存储单元,这种架构设计可以实现一个高性能且低功耗的AI芯片,比如Intel ETANN芯片。在全硬件实现方案中上一层输出数据和权重相乘,相乘的结果再相加,然后再经过一个激活函数输出到下一层计算。这种架构设计将计算和存储紧密的耦合在一起,使得芯片在进行高速计算的同时由能避免大规模的数据访存,在提高整体计算性能的同时也降低了功耗。

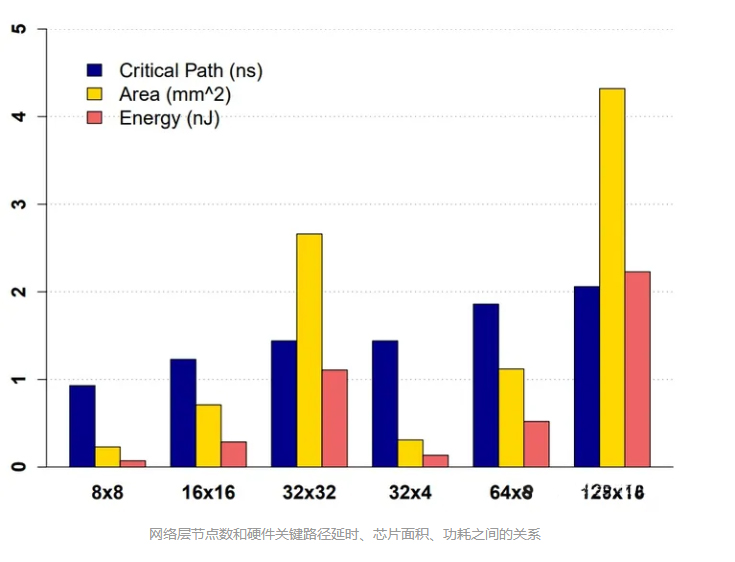

全硬件实现方案具有设计简单、计算性能高、功耗低等特定,但它仅适用于小规模的神经网络计算,对于大型神经网络的计算存在明显的硬件限制。如图所示,当网络层的节点为16 x 16时,芯片面积只需要0.71 ,但当网络层的节点为32 x 32时,芯片面积则需要2.66 ,当网络层包含的节点进一步增大时所需要的芯片面积和能耗将大幅提升,所以直接映射方案已经不能满足当前规模越来越大的深度学习算法发展。

ASIC芯片的设计基本都是针对领域计算特性,围绕访存、能耗、吞吐率、成本、灵活性等指标进行优化和设计。随着深度学习算法发展,神经网络深度和规模越来越大,网络结构也从CNN为主的网络架构设计逐渐演变到Transformer为主的网络架构设计,算法对芯片需求也从计算密集性过度到存算密集性,AI芯片的设计也从偏计算走向存算一体的混合计算模式。具体体现在:

底层架构:从存算分离到存算一体设计。

数据通信:从高速数据通信到低精度计算和稀疏计算。

模型设计:从模型-硬件独立设计到模型-软硬件联合优化设计。

时域计算

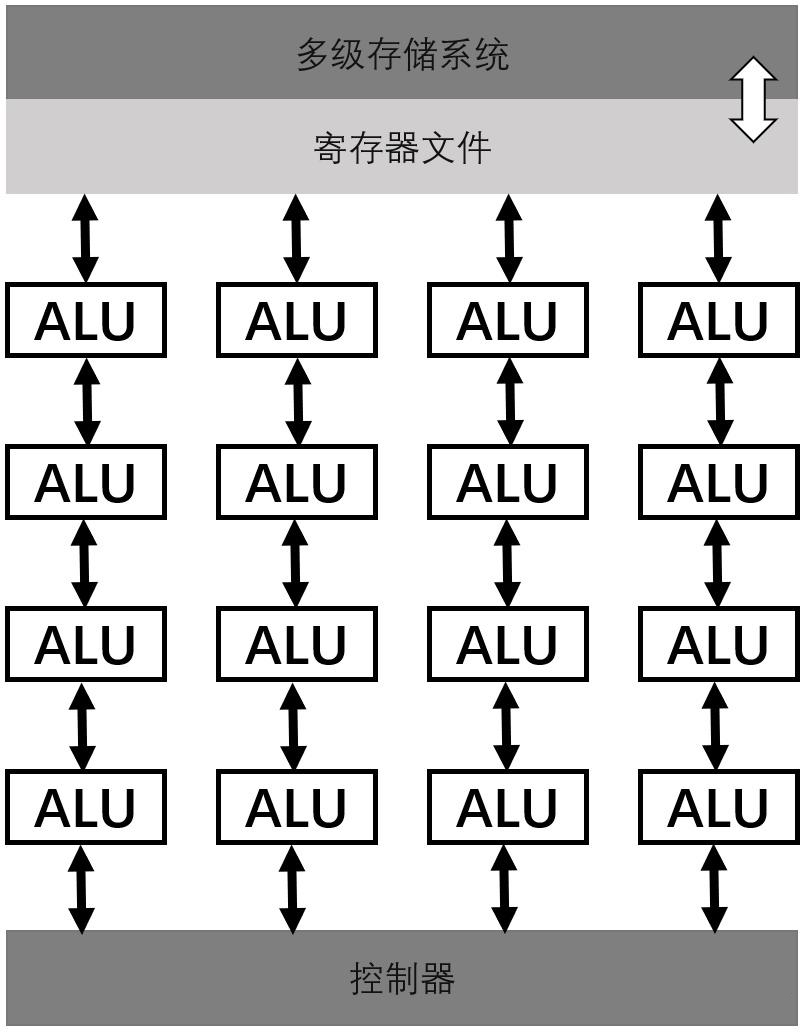

时域计算指采用定制化指令集的专用处理器,其通过指令流水线对逻辑计算单元(Arithmetic Logic Unit, ALU)和存储系统进行统一管理和调度,ALU流水线从存储系统中读取数据,经过多级流水线处理后将最终运算结果写回存储系统。深度学习神经网络模型主要是大量的线性代数运算,而控制流程则相对简单,所以,AI芯片通常采用高度并行的计算架构设计,为了提高处理器并行计算能力,需要让一条指令同时针对多个数据元素执行相同的操作。基于深度学习的计算流程相对固定的特点,多个固定步骤的计算可以通过多个ALU流水线设计来实现高效计算,比如矩阵运算中的多数据乘累加计算。

时域计算架构

中国科学院计算技术研究所的DianNao系列架构设计是一种典型的时域计算架构设计。DianNao系列的芯片主要包含三部分:神经功能单元(Neural Functional Unit, NFU)、三个不同功能片上存储区和控制器。NFU和存储通过控制器的指令进行调度,运算核心NFU按照卷积运算流程划分为乘法功能段NFU1、加法功能段NFU2以及非线性激活函数功能段NFU3的三级流水线设计。DianNao针对深度学习的计算特性进行定制设计,使其在AI计算上能够获得比通用处理器更高的能效。

空域计算

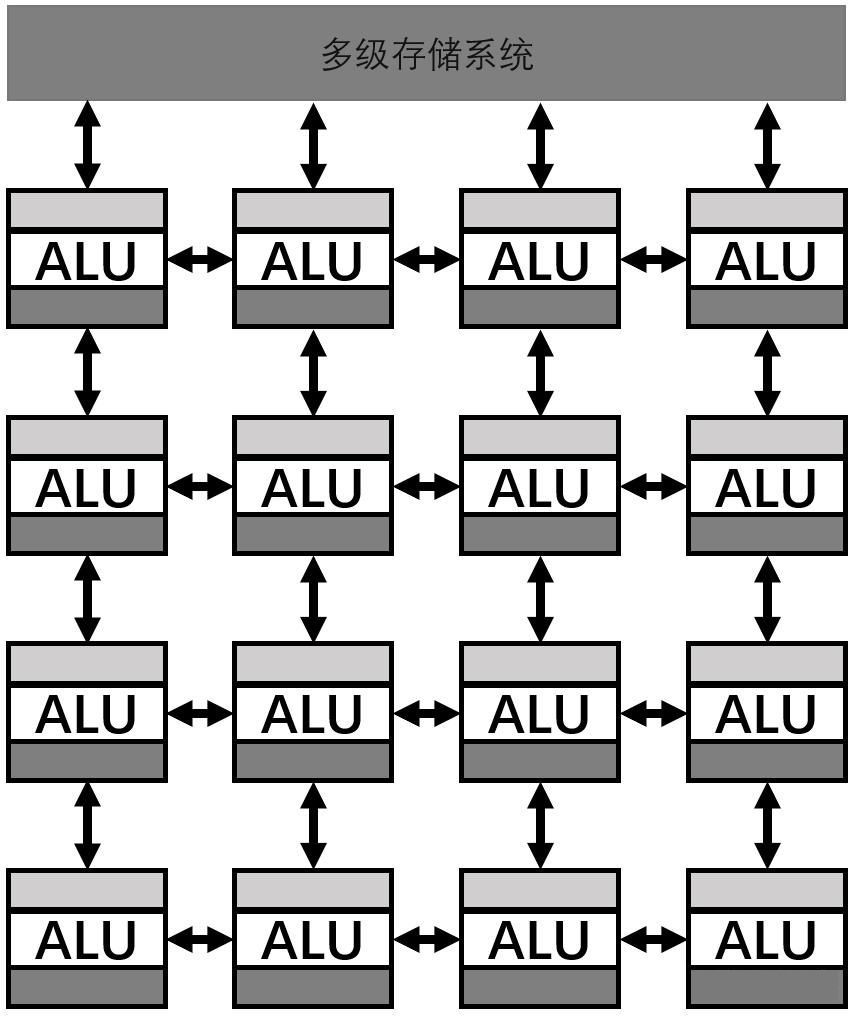

与时域计算不同,空域计算中每个计算单元PE都具有独立的控制单元和存储单元。空域计算架构通常由一维或二维PE阵列构成,每个PE内部自带控制器和缓存,PE之间可以直接传递数据。除此之外,还有片上全局缓存、片外DRAM等不同层次存储构成的多级存储系统。空域计算架构利用大量PE阵列完成高效的并行计算,通过PE之间的数据流动减少处理器与主存之间的通信次数。

空域计算架构

Google TPU (Tensor Processing Unit)是空域计算架构的典型代表之一,它包含一个256x256个MAC组成二维矩阵乘法阵列,此外其内部还集成了归一化/池化单元和非线性激活单元等。TPU的二维矩阵乘法阵列按照脉动阵列(Systolic Array)方式互连,PE计算的数据来自前一个时钟周期中相邻PE的计算结果,PE在当前时钟周期计算得到的结果则按同样的方式流入相邻的PE在下一个时钟周期参与计算,由于数据在阵列中不同PE之间的流动像血液在血管中脉动传输一样按照规定的节奏进行传递和计算,所以称之为脉动阵列架构。

数据复用

数据复用指在计算过程中对同一数据进行重复使用以减少对存储器访问次数。深度学习中的数据复用通常包括:输入数据复用、输出数据复用和权重数据复用。例如,在DianNao架构中SB和NBin分别用来存储权重和数据神经元数据,NFU单元用来进行点乘和累加的运算,输出数据存储在NBout中,在计算过程中输出数据会先输出到缓存器中直到完成所有的部分和的累加后才会被写回。

存储优化

弥补计算单元和存储器之间的差距的途径主要包括:

高带宽的数据通信技术,使用更先进的通信技术提高数据传输的效率。

通过增加片上存储容量让数据更靠近计算单元,减少数据在计算单元和内存之间的搬运成本。

使用高密度片上存储技术,例如eDRAM存储单元由晶体管和电容构成,相比于SRAM具有更高的存储密度。

使用三维集成(3D Integration)存储器技术将多块存储器在垂直方向上堆叠起来,以获得更大存储容量。

直接在存储器内部实现计算,即存内计算,目前受限制造工艺和计算精度等问题,其应用范围还比较有限。

郑重声明:文中仅代表作者观点,不代表本公司观点,本文版权归原作者所有,转载文章仅为传播更多信息之目的,如作者信息标记有误,请第一时间联系我们修改或者删除,感谢您的关注!